Product Summary

The UPD4564841G5-A80-9JF is a high-speed 67,108,864-bit synchronous dynamic random-access memory. The UPD4564841G5-A80-9JF is achieved high-speed data transfer using the pipeline architecture. All inputs and outputs are synchronized with the positive edge of the clock. The UPD4564841G5-A80-9JF is compatible with Low Voltage TTL (LVTTL). The device is packaged in 54-pin TSOP.

Parametrics

UPD4564841G5-A80-9JF absolute maximum ratings: (1)Voltage on power supply pin relative to GND, VCC, VCCQ: –0.5 to +4.6 V; (2)Voltage on input pin relative to GND, VT: –0.5 to +4.6 V; (3)Short circuit output currentm IO: 50 mA; (4)Power dissipation, PD: 1W; (5)Operating ambient temperature, TA: 0 to +70℃; (6)Storage temperature, Tstg: –55 to +125℃.

Features

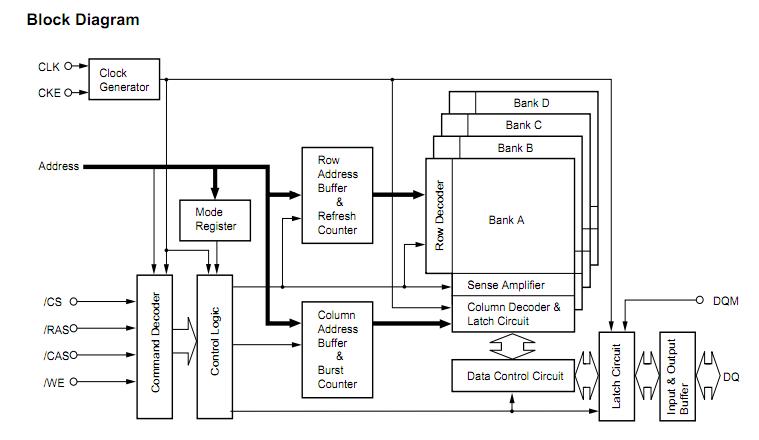

UPD4564841G5-A80-9JF features: (1)Fully Synchronous Dynamic RAM, with all signals referenced to a positive clock edge; (2)Pulsed interface; (3)Possible to assert random column address in every cycle; (4)Quad internal banks controlled by A12 and A13 (Bank Select); (5)Byte control (x16) by LDQM and UDQM; (6)Programmable Wrap sequence (Sequential / Interleave); (7)Programmable burst length (1, 2, 4, 8 and full page); (8)Programmable /CAS latency (2 and 3); (9)Automatic precharge and controlled precharge; (10)CBR (Auto) refresh and self refresh; (11)x4, x8, x16 organization; (12)Single 3.3 V ± 0.3 V power supply; (13)LVTTL compatible inputs and outputs; (14)4,096 refresh cycles/64 ms; (15)Burst termination by Burst stop command and Precharge command.

Diagrams

|

UPD42S16800L |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UPD431000A-X |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UPD4364CX-10 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UPD441000L-X |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UPD4416001 |

Other |

|

Data Sheet |

Negotiable |

|

||||

|

UPD4416004 |

Other |

|

Data Sheet |

Negotiable |

|

||||

(China (Mainland))

(China (Mainland))